Semiconductor manufacturers are investigating maskless patterning technologies to ease costs and reduce fabrication times for the next generation of integrated circuits.

Hank Hogan, Contributing Editor

When Walt Trybula looks at the future of semiconductor manufacturing, he sees problems. Such foresight is part of his job as a senior fellow at the Austin, Texas-based semiconductor research consortium Sematech. Besides looking forward to spot difficulties, Trybula also is supposed to find fixes to looming issues before they become catastrophes.

Among other things, he's worried about masks. These are used to pattern each layer of an integrated circuit, and 30 or more of them may be in the mask set for a given chip. Those masks also have others in the industry concerned.

“The masks have been getting more complex,” Trybula said. That complexity, he noted, results in higher costs and slower deliveries, which make it more difficult to ramp up new designs in the most advanced semiconductor processes.

So the industry is looking at alternatives. The idea is to have a patterning tool that directly transfers design data to silicon wafers for at least the low-volume, prototyping phase of production. This could have a payoff in the millions, he said.

“If we reduce the number of masks at the critical levels, and we do it with a maskless approach, we have the potential for removing the initial cost,” he added.

At present, there are schemes for doing maskless manufacturing optically and with beams of charged particles. Another proposal is to eliminate masks and stamp out chips using a mold. At the moment, all three approaches have potential and problems.

Patterning at a price

The conventional way to build an integrated circuit is to use a mask, which is made up of a transparent material, such as fused silica. Lines, rectangles and other features of an opaque material, such as chrome, cover this substrate. A photolithographic tool shines a laser through the mask and onto a wafer, where a photosensitive polymer cross-links and becomes tough enough to withstand subsequent processing. This polymer is used to pattern underlying layers and, ultimately, to transfer what was on the mask into a layer on the chip. Photolithographic tools can churn out 100 or more 300-mm wafers per hour, with each holding hundreds of chips.

The chrome is written on the mask itself using an electron beam under computer direction. Because the mask will be used over and over again, it must be perfect. Masks and the circuit layer they embody must also be correctly designed so that the circuit functions as it should. According to Trybula, four out of 10 mask layers meet these design criteria and are written only once. The same isn’t true for all layers, especially some of the most critical and intricate.

“When you get to the other end, 15 percent of the masks end up being written four or more times, so you’ve got this high number of writes,” he said.

As process feature sizes have shrunk from the 130 nm of a few years ago to the 65 nm of today’s state-of-the-art, the masks have grown ever more complex. Circuits are bigger and denser. The need to pattern smaller features has led to the use of phase-shift corrections and other optical techniques.

These trends make masks more expensive. An analysis by Sematech put the cost of a mask set at the 130-nm node at about $700,000. At the 90-nm node, the figure climbed to about $1.5 million. The 65-nm node, which is just entering production, will double that again, to about $3 million. Counting rewrites, the cost could be upward of $8 million for every integrated circuit design.

The squeeze play

At the same time, the industry faces an economic squeeze. Klaus Rinnen, managing vice president for the semiconductor manufacturing and design research group at the technology market analysis firm Gartner Inc. of Stamford, Conn., noted that the revenue per area of silicon — the dollars brought in for every square inch of integrated circuit produced — has dropped steadily over the past 10 years. So costs, both direct and indirect, must be wrung out of the process.

For semiconductor manufacturers, time spent waiting for masks to be produced — and, perhaps, made again because of a design flaw or other error on a particular level — translates into extra expense and lost time. Of the two, Rinnen believes that the time lost is the more costly.

“It’s much more crucial that the time to market is shortened, that ramps to product are steepened in order to get more product out at [an] earlier time,” he said.

He added, however, that it’s unlikely that a maskless approach will be used anytime soon for high-volume production, such as for memory chips. It’s much more likely that a maskless technique will be used for the low-volume production of a niche product or for the early, prototyping stages in the development of a high-volume part.

With this method, costly mask spins would be avoided. As volume ramped up, manufacturing would transition to something like the masked processes currently used.

Achieving a smooth transition to masked processing places some constraints on any maskless technology. In particular, whichever resist is used ideally should be the same in both prototyping and production. If that’s the case, then the maskless tool can be swapped for the standard photolithographic machine without disturbing any other part of the manufacturing process.

“If I can do the prototyping with the same material and the same processes I use in production, I have really gained on the whole process,” Trybula said. “I’ve cut the cycle time down, and I don’t have to requalify for production.”

For the optical maskless approach, there are a number of promising technologies. One is zone-plate lithography. Developed at the Cambridge-based Massachusetts Institute of Technology, this technique is being commercialized by the nearby LumArray Inc.

In zone-plate lithography, a large array of microfabricated diffractive lenses focus a single beam of light onto a substrate as an array of microbeams. Computer-controlled micromechanical systems turn the light on or off as the array scans across the die. In effect, the pattern is transferred to the wafer using a series of on and off dots.

Although LumArray is less than a year old, the zone-plate technique has been used at MIT to pattern lines with widths of less than 85 nm. The company asserts that linewidths of 20 nm can be achieved with a light source of about 13 nm, the wavelength of the next generation of lithographic tools. Co-founder David Michaud has said that its products are aimed at niche markets and at those who need a cheap machine instead of a fast one.

Array of micromirrors

Another optical maskless lithography scheme is being developed by Lucent Technologies of Murray Hill, N.J., under a contract from the US Department of Defense. Lucent is hoping that the four-year, $10 million contract will allow it to leverage its spatial light modulator technology — which is based on microelectromechanical systems (MEMS) and which has been used in telecommunications — into a new line of maskless lithography tools.

Figure 1. Lucent Technologies will take existing micromirror technology and shrink it several times. Packed into an array of 10 million elements, the 3-μm-diameter micromirrors will move up and down to enable the maskless imaging of a semiconductor circuit.

According to Vladimir Aksyuk, technical manager in Lucent’s microsystems integration group, this approach will make use of an array of micromirrors (Figure 1). Unlike those found in the company’s telecommunications products or in commercial displays, these won’t be gimbaled to pivot about an axis. “They’d be moving just up and down out of the plane of the substrate,” he said. “The ultimate size that we’re shooting for is 10 megapixels, or 10 million mirrors, at the pitch of 3 μm.”

The goal is to produce 50-nm features by bouncing ultraviolet radiation off the mirrors, which will move up and down by 100 nm or so to create constructive and destructive interference between adjacent sites. The resulting bright and dark spots will be optically reduced by a factor of approximately 200 to create features that are much smaller than the mirrors.

Electrons and other beams

Although Aksyuk believes that the project will be successful, there are challenges to be overcome. The number of mirrors in the array is much larger and the mirrors quite a bit smaller than Lucent’s current technology, which has 10-μm micromirrors. Another issue will be integrating the electronics into the chip. This will entail building millions of transistors on the silicon before constructing the micromirrors, which will sit atop the controlling electronics. One thing he is not worried about is reliability: Properly constructed MEMS can be cycled billions of times without a noticeable change in their performance.

Another class of maskless contenders involves beams of charged particles. This technology uses an electron or other charged particle to directly write data onto a resist-coated wafer. A similar process is used today to produce most masks, and one possibility would be to simply skip the intermediate mask-writing step. Instead, the electron-beam (or “e-beam”) machine, under computer control, would create the needed features directly on the wafer.

Of all the maskless techniques, direct-write electron-beam technology has the longest history of use. It’s also the only maskless technology today producing commercial silicon. San Jose, Calif.-based eAsic Corp. uses it at its foundry partners to customize single-circuit layers for clients and foundry customers.

Alon Kapel, vice president of European operations, noted that the company does this only for an interconnect layer that takes up less than 3 percent of the chip area versus the more than 40 percent found in other layers. Every other layer is produced using a mask.

“This allows eAsic a very efficient use of the e-beam direct-write process, resulting in about 10 times higher machine throughput and, therefore, enabling shorter turnaround time and lower cost,” Kapel explained.

When customers want a fully masked process to enable increased volumes, they need to order and qualify only the mask for the single interconnect layer. Everything else remains the same. It’s even possible to combine different projects into one wafer so that each bears only a part of the total cost of the silicon.

Traditionally, electron-beam technology has been seen as slow and costly. What’s more, transitioning to production is not easy because the resist used in an electron-beam machine usually is not the same as that used in a photolithographic tool. These drawbacks are particularly

evident when multiple layers are involved. Some companies that once used the direct-write approach thus have moved away from the technology, opting instead to employ it for customization of chips.

Stamp of approval

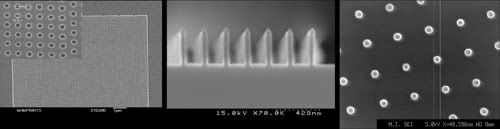

One company tackles the problem in a different way. Instead of a mask, Molecular Imprints Inc. of Austin, Texas, offers a potentially simpler, less-expensive and quicker means to produce molds. Through a process called step-and-flash imprint lithography, this transparent template patterns the wafer (Figure 2).

Figure 2. In Molecular Imprints Inc.’s step-and-flash imprint process, a transparent template is oriented to a substrate, and drops of resist are dispensed between them. The template is lowered, and the resist is polymerized via UV exposure. The template is removed and stepped to another location, and the process is repeated.

During this procedure, a drop-dispensed, low-viscosity resist fills the 50- to 100-nm gap as the mold is brought close to the wafer surface. In the next step, an ultraviolet curing light shines through the mold. The template then is removed with the help of a release layer, leaving the pattern on the wafer. Molecular Imprints estimates that the templates used must be cleaned every 4000 or so stampings.

Because the approach doesn’t use projection optics, the templates don’t have the expensive and throughput-degrading enhancements needed by masks. Step-and-flash imprinting also doesn’t require expensive ultraviolet lasers.

“With photolithography, the wavelength of light directly implies how small the features you can get,” said Michael Falcon, business development manager at the company. “With ours, it’s a micromolding process. The wavelength of light is used only for the curing. You can actually tune that wavelength, so we would cure out at 500 nm.” That, he added, could be important in cases in which a biological system is involved.

2005 generation of tools

Unlike electron-beam, micromirror or microlens lithography, step-and-flash imprinting is capable of high throughput at sub-50-nm feature sizes (Figure 3). The current generation of the company’s tools is aimed at research and development or at low-level manufacturing, and so the focus has been on pattern alignment and not throughput. The next generation of tools, due out early in 2005, will come closer to the speeds achieved by current photolithographic machines.

Figure 3. Scanning electron micrographs reveal 40- to 65-nm holes, lines and pillars produced by step-and-flash imprinting. These test structures are similar to features found on advanced integrated circuits, indicating that the process could be used to produce chips.

However, even the new generation won’t use the same resist as a photolithographic mask. A traditional photolithographic resist is fairly viscous and usually is spread in a thin, even layer over a wafer by spinning the wafer at a high speed. Step-and-flash imprinting, in contrast, uses a waterlike resist.

Although all of these techniques have potential, they also raise some serious questions involving their throughput and integration with the standard masked process. Because of this, Sematech has called an industrywide meeting on maskless technology to evaluate the contenders.

As to what the consortium hopes to accomplish with this meeting, scheduled to take place soon, Trybula pointed to the rapid adoption and impending rollout of immersion lithography, designed to extend the life of current lithographic technologies. The embrace of the technique was spurred by a looming problem.

Today, maskless patterning is just such another impending issue.